PYTANIA TESTOWE 20080615 231720 1 PROCESOR MA ARCHITEKTURĘ AKUMULATOROWĄ

ZAŁĄCZNIK 3A DO ZAPYTANIA OFERTOWEGO OŚWIADCZENIE OFERENTA O(ZAŁĄCZNIK NR 2 DO ZAPYTANIA OFERTOWEGO) U M O

0DPOWIEDZI NA ZAPYTANIA WYKONAWCÓW ZADANIE PN BUDOWA PRZYDOMOWYCH OCZYSZCZALNI

0Zalacznik_Nr_1_do_Zapytania_ofertowego

18POIR2019 WARSZAWA 17122019R ODPOWIEDZI NA PYTANIA I MODYFIKACJA ZAPYTANIA

19042010 UCZESTNICY POSTĘPOWANIA NR 05P132010 DOTYCZY ODPOWIEDZI NA PYTANIA

Pytania testowe

|

Pytania testowe |

2008-06-15 23:17:20 |

Procesor ma architekturę akumulatorową. Wskaż rozkazy spoza listy tego procesora: (JB 47-49)

|

|

|

|

|

|

|

|

|

|

|

|

Procesor ma architekturę rejestrową L/S. Wskaż rozkazy spoza listy tego procesora: (JB 47-49)

|

|

|

|

|

|

Procesor ma architekturę rejestr-pamięć. Wskaż rozkazy spoza listy tego procesora: (JB 47-49)

|

|

|

|

|

|

Linie bufora pamięci podręcznej z odwzorowaniem bezpośrednim są aktualizowane w trybie „no allocate on write”. Wymiana linii jest skutkiem: (JB 198-199)

|

|

|

|

|

|

Linie bufora pamięci podręcznej z odwzorowaniem bezpośrednim są aktualizowane w trybie „allocate on write”. Chybienie podczas zapisu: (JB 198-199)

|

|

|

|

|

|

Aktualizacja linii bufora pamięci podręcznej o organizacji asocjacyjnej następuje w trybie „no allocate on write”. Chybienie podczas odczytu po uprzednim unieważnieniu całego bufora: (JB 198-199)

|

|

|

|

|

|

Aktualizacja linii bufora pamięci podręcznej o organizacji blokowo-skojarzeniowej (wielodrożnej) następuje w trybie „no allocate on write”. Chybienie podczas odczytu: : (JB 198-199)

|

|

|

|

|

|

Aktualizacja linii bufora pamięci podręcznej o organizacji wielodrożnej (blokowo-skojarzeniowej) następuje w trybie „allocate on write”. (Bufor jest wypełniony). Chybienie podczas zapisu:

|

|

Wywołuje efekt migotania |

|

|

powoduje zapis linii bufora zapisu |

|

|

|

Statystyczna prognoza rozgałęzień (skoków):

|

|

|

|

|

|

|

|

|

|

|

|

Dynamiczna prognoza rozgałęzień (skoków): (JB 226-228)

|

|

|

|

|

|

|

|

|

|

|

|

Skutkiem chybienia w buforze prognozy skoków BTB jest:

|

|

|

Skutkiem trafienia w buforze prognozy skoków BTB jest:

|

|

|

Bufor prognozy skoków BTB jest aktualizowany: (JB 226-228)

|

|

|

|

|

|

Linia bufora BTB zawiera następujące informacje: (JB 226-228)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rozmiar logicznej przestrzeni adresowej zależy od:

|

|

|

|

|

|

Maksymalny rozmiar wirtualnej przestrzeni adresowej zależy od: (JB: 141-143; STAL: 296)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W bloku aktywacji funkcji na stosie są umieszczone: (JB: 114-115)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W bloku sterującym (PCB) każdego aktywnego procesu przechowywane są:

|

|

|

|

|

|

|

|

|

|

|

|

Pełny kontekst pamięci procesu jest przechowywany:

|

|

|

|

|

|

|

|

|

|

|

|

Charakterystycznymi cechami architektury klasy CISC są:

|

|

|

|

|

|

|

|

|

|

|

|

Charakterystycznymi cechami architektury klasy RISC są:

|

|

|

|

|

|

|

|

|

|

|

|

Przekroczenie zakresu w odejmowaniu w kodzie znak-moduł jest sygnalizowane:

|

Jako przeniesienie równe 1 |

Jako bit znaku równy 1 |

|

Jako wskaźnik nadmiaru równy 1 |

Gdy znaki argumentów są jednakowe |

Przekroczenie zakresu w dodawaniu i odejmowaniu w naturalnym kodzie binarnym sygnalizuje:

|

|

|

|

|

|

Przekroczenie zakresu w dodawaniu i odejmowaniu w kodzie uzupełnieniowym U2 sygnalizuje:

|

|

|

|

|

|

Wystąpienie nadmiaru w dodawaniu w kodzie uzupełnieniowym U2 jest sygnalizowane jako:

|

|

|

|

|

|

W formacie zmiennoprzecinkowym pojedynczej precyzji liczbami zdenormalizowanymi są:

|

|

|

|

|

|

|

|

|

W formacie zmiennoprzecinkowym pojedynczej precyzji liczbami znormalizowanymi są:

|

|

|

|

|

|

|

|

|

|

|

|

Skutkiem braku żądanej strony w pamięci jest:

|

|

|

|

|

|

Przerwania nieprecyzyjne są skutkiem: (JB:130-131)

|

|

|

|

|

|

Przerwania precyzyjne są skutkiem: (JB:130-131)

|

|

|

|

|

|

|

|

|

|

|

|

2 PYTANIA EGZAMINACYJNE Z PEDIATRII ( FIZJOTERAPIA – SEMESTR

3.-zal.-nr-2-do-zapytania-ofertowego---wzor-umowy-1639665310

5 ZAŁĄCZNIK NR 2 DO ZAPYTANIA OFERTOWEGO NR OKEREG122016

Tags: akumulatorową, architekturę, procesor, pytania, 20080615, testowe, 231720

- B&R ROZŠIŘUJE X20 IO SYSTÉM O MODULY S PROTOKOLEM

- (IME I PREZIME) (ADRESA) TELMOB OIB

- HTTPBREMAIKFREEFR 2 A VIZ GOUERE SIZHUN 27 2007 BREMAIKFREEFR

- ZWIĄZEK HARCERSTWA POLSKIEGO KATOWICE 26102006R KOMENDANT ŚLĄSKIEJ CHORĄGWI ROZKAZ

- HELL HOUSE BACK TO BACK THEATRE PRESENTED BY

- GUIDELINES FOR PPE ENSEMBLE SELECTION –POSTED APRIL 2011 GUIDELINES

- CARSON HIGH SCHOOL – TELEPHONE DIRECTORY 20152016 REVISED 8202015

- RADICACIÓN N° 11001020300020200058000 AC6652020 RADICACIÓN N° 11001020300020200058000 BOGOTÁ DC

- KRITERIJI ZA ODABIR PONUDE KRITERIJ ZA ODABIR PONUDE JE

- FOLLETO INFORMATIVO NO19 INSTITUCIONES NACIONALES DE PROMOCIÓN Y PROTECCIÓN

- INVESTIGATING SILVER NITRATE TITRATIONS BACKGROUND SILVER NITRATE CAN

- ABANDONATU NAHIAREN DEKLARAZIOA DECLARACIÓN DE VOLUNTAD DE ABANDONO

- PASAR AL CONTENIDO PRINCIPAL TOGGLE NAVIGATION JUNTA DE COMUNIDADES

- 1 VACACIONES EN ESPAÑA KV 15 EL PRETÉRITO PERFECTO

- DOKTORA PROGRAMINA GİRİŞ DEĞERLENDİRME PROTOKOLÜ ENSTITÜMÜZ ANABILIM DALINDA

- INTERNE UNFALLANZEIGE AN ÖRTLICHE SICHERHEITSFACHKRAFT (SIEHE AUSHANG) SEITE 2

- PER QUALE MOTIVO SONO STATE ESCLUSE DAL REGISTRO LE

- MINISTERSTWO KULTURY I DZIEDZICTWA NARODOWEGO JAKO OPERATOR PROGRAMU „KONSERWACJA

- SISTEMA OPERATIVO WINDOWS XP HOME – CURSO DE AULACLIC

- GHTH 100 PERSONAL WELLNESS DR TERRI PRODOEHL PRODOERTJMUEDU IT

- ANEXO 2º ETAPA EDUCACIÓN PRIMARIA EDUCACIÓN ARTÍSTICA INTRODUCCIÓN EL

- CORROSION CORROSION IS THE WEARING AWAY OF METALS DUE

- RAMIRO VILLASEÑOR Y VILLASEÑOR HISTORIADOR JALISCIENSE OBSERVADOR ACUCIOSO ÁVIDO

- FIJA TEXTO REFUNDIDO COORDINADO SISTEMATIZADO Y ACTUALIZADO DE LA

- JORNADA INFORMATIVA RÉGIMEN DE ENTRADA PERMANENCIA Y TRABAJO DE

- ¿POR QUÉ DEBO MATRICULARME? AUTOR BIOQ ANA M SOLUSSOGLIA

- GUÍA DEL CANDIDATO – MUNDUS LINDO SEGUNDA COHORTE INTRODUCCIÓN

- USKOK JE NAKON PROVEDENE ISTRAGE PRED ŽUPANIJSKIM SUDOM U

- DOA MAJLIS ANUGERAH CEMERLANG PEGAWAI بِسْمِ اللهِ الرَّحْمَنِ الرَّحِيْمِ

- NITRATE REMOVAL USING WASTED INDUSTRIAL IRON POWDER 1YONG H

GT N°18 “UNIVERSIDAD HISTORIA RECIENTE MEMORIA COLECTIVA Y TRABAJO

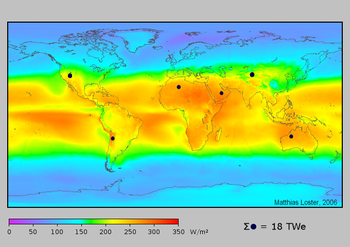

2 ENERGÍA SOLAR DE WIKIPEDIA LA INSTALACIÓN DE

2 ENERGÍA SOLAR DE WIKIPEDIA LA INSTALACIÓN DE CGE GHG INVENTORY HANDBOOK (NAI) INDUSTRIAL PROCESSES SECTOR –

CGE GHG INVENTORY HANDBOOK (NAI) INDUSTRIAL PROCESSES SECTOR – EVANGÉLIKUS KÖZÉPISKOLAI KOLLÉGIUM PEDAGÓGIAI PROGRAM KÉSZÍTETTE HEGYVÁRINÉ PAULÓ MÁRIA

EVANGÉLIKUS KÖZÉPISKOLAI KOLLÉGIUM PEDAGÓGIAI PROGRAM KÉSZÍTETTE HEGYVÁRINÉ PAULÓ MÁRIACONFERENCE ON JEWISH MATERIAL CLAIMS AGAINST GERMANY INC GRANT

ACTA DE LA JUNTA EXTRAORDINARIA DE LA COMUNIDAD DE

CORPORACION MONTE ACONCAGUA LICEO BICENTENARIO MIXTO LOS ANDES UNIDAD

CORPORACION MONTE ACONCAGUA LICEO BICENTENARIO MIXTO LOS ANDES UNIDADESCRIBIENDO RÚBRICAS UTILIZANDO LA TAXONOMÍA DE BLOOM NIVEL ÉNFASIS

PLEASE NOTE TO MAINTAIN THE INTEGRITY OF THE DATA

PLEASE NOTE TO MAINTAIN THE INTEGRITY OF THE DATAINSTITUTO SUPERIOR DE FORMACIÓN DOCENTE SALOME UREÑA RECINTO EMILIO

HR EUROPSKI GOSPODARSKI I SOCIJALNI ODBOR REX389 ULOGA CIVILNOG

HR EUROPSKI GOSPODARSKI I SOCIJALNI ODBOR REX389 ULOGA CIVILNOG M AIRIE DE BANDRÉLÉ COMMUNIQUÉ DE PRESSE TITRE

M AIRIE DE BANDRÉLÉ COMMUNIQUÉ DE PRESSE TITRE PÉCSI TUDOMÁNYEGYETEM MŰVÉSZETI KAR KÉPZŐMŰVÉSZETI MESTERISKOLA A MONUMENTÁLIS TUSFESTÉSZET

MARK 929 WHAT DOES THE TRANSFIGURATION TEACH US? FEBRUARY

COMMENT SUBMISSION FORM PUBLICLY NOTIFIED APPLICATION FOR LEASES

COMMENT SUBMISSION FORM PUBLICLY NOTIFIED APPLICATION FOR LEASESNOTES ON TONIGHT’S PROGRAM THE SUCCESS OF THE BALLET

COMPLEMENTARY AND ALTERNATIVE MEDICINE (CAM) COMPLEMENTARY AND ALTERNATIVE MEDICINE

TERMS OF REFERENCE OF THE EAST MIDLANDS SPECIALIST POSTGRADUATE

EVS A CATALYST FOR LECTURE REFORM BY ABRUCE SCHOOL

AQC ARBEITSGEMEINSCHAFT FÜR QUALITÄTSSICHERUNG IN DER CHIRURGIE AQC GESCHÄFTSSTELLE

AQC ARBEITSGEMEINSCHAFT FÜR QUALITÄTSSICHERUNG IN DER CHIRURGIE AQC GESCHÄFTSSTELLE