6ZÁKLADNÍ VLASTNOSTI LOGICKÝCH ČLENŮ OBVODY RTL DTL TTL CMOS

LOGICKÉ OBVODY

6.Základní vlastnosti logických členů, obvody RTL, DTL, TTL, CMOS, ECL ... - provedení, princip činnosti

S polovodičovými prvkami můžeme realizovat libovolně složité spínací funkce ve všech zařízeních na zpracování informací, například v číslicových počítačích, v řídících obvodech automatizovaných průmyslových zařízeních, v telefonních ústřednách apod.

Činnost logických obvodů je založená na základních pravidlech tzv. výrokové logiky, která pracuje s výrokami, které mohou být pravdivé ( přiřazujeme jim log.1 ) anebo nepravdivé (přiřazujeme jim log.0.) Z fyzikálního hlediska můžeme teda zpracovávat informace v logických obvodech ve formě signálů (buď log.1 anebo log.0).

Základní logické členy

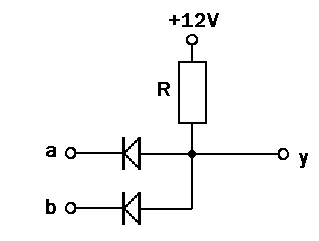

Součinový člen - na výstupu je log. 1 (+12V) pouze tehdy, jsou-li na obou vstupech log. 1

je-li na některém z vstupů log.0 ( nulové napětí ), na výstupu je nulové

napětí ( log 0 ) ( viz tabulka a schéma zapojení )

|

b |

a |

y |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

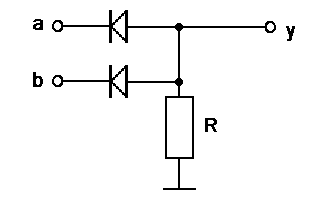

Součtový člen - na výstupu je log. 0 pouze tehdy jsou-li na obou vstupech log.0

- je-li na některém ze vstupů log.1, je na výstupu log.1

( viz tabulka a schéma zapojení )

|

b |

a |

y |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

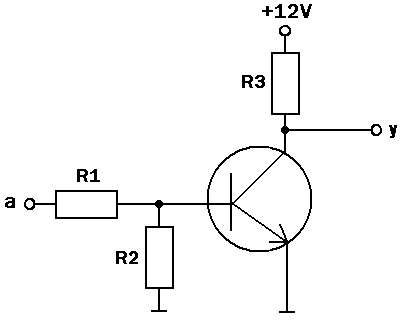

Invertor - log.1 na vstupu dává na bázi tranzistoru napětí mezi 0-12V. Tranzistor je otevřen

a na výstupu je nulové napětí – log. 0

- je-li na vstupu nulové napětí, je toto napětí i na bázi tranzistoru, tranzistor je zavřen

( nevede ) a na vástupu je plné napětí 12V – log.1

|

a |

y |

|

0 |

1 |

|

1 |

0 |

Rozdělení logických obvodů

RTL - tranzistorové logické obvody s odporovou vazbou (Resistor-Transistor-Logic).

DTL - logické obvody s diodovou logikou (Diode Transistor Logic).

TTL - logické obvody s transistorovou logikou (Transistor-Transistor-Logic)

Integrované obvody RTL

Tyto obvody jsou dnes již spíše historickou záležitostí. ( tato technologie má nejhorší statické a dynamické vlastnosti, byla dražší a méně spolehlivější než IO – v současné době se již nepoužívá ).

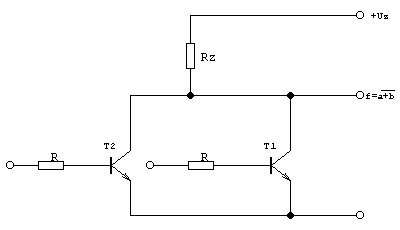

V zapojení uvedeném na obrázku dole se používá kladného napájecího napětí, takže při kladné logice bude obvod realizovat logickou funkci NOR. Při vstupní úrovni 0 budou oba tranzistory uzavřené a na výstupu bude úroveň 1. Otevřením alespoň jednoho tranzistoru (úroveň 1 na jeho vstupu) klesne výstupní napětí na úroveň 0

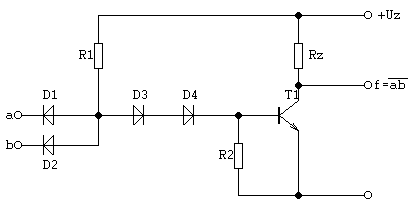

Integrované obvody DTL

Jsou to obvody s diodami na vstupech a s tranzistorem na výstupu. Na obrázku je zapojení integrovaného obvodu realizujícího funkci NAND

Vstupní diody spolu s odporem R1 pracují jako diodový logický součin, jehož výstupní funkci neguje tranzistor T1, zapojený jako invertor.

Jsou-li všechny vstupní svorky na úrovni 1, tranzistor T1 se přes posouvací diody D3 a D4 otevře a na výstupu obvodu je úroveň 0.

Přivedením úrovně 0 alespoň na jeden vstup obvodu budou anody vstupních diod D1 a D2 téměř na nulovém potenciálu a tranzistor T1 se uzavře.

Na výstupu obvodu bude úroveň 1. Tzv. posouvací diody D3 a D4 zajišťují dokonalé uzavření tranzistoru a zvyšují šumovou imunitu obvodu tím, že svým prahovým napětím zvyšují nutnou napěťovou úroveň pro otevření tranzistoru.

Rychlé uzavření tranzistoru zajistíme rychlým odvedením přebytečného náboje z jeho báze. V integrovaných obvodech se proto používá zapojení podle obr. dole.

Tranzistor T1 pracuje v nenasyceném stavu (čehož je dosaženo připojením kolektoru mezi odpory R1 a R2), zvyšuje též proudové zesílení, a tak umožňuje zvýšit logický zisk obvodu

Napájecí napětí těchto obvodů bývá asi 5 V, logický zisk N=10, šumová imunita asi 0,8 V, zpoždění 10 až 30 ns.

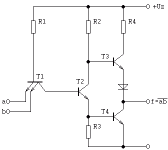

TTL obvody

Je to nejrozšířenější a nejrozmanitější technologie. Vstupy a výstupy jsou realizovány tranzistory. Na vstupu je tranzistor s více emitory.

Základ tranzistorových logických obvodů s transistorovou logikou (TTL = Transistor-Transistor-Logic) tvoří tranzistor s vícenásobným emitorem, který umožňuje realizovat logické funkce. Při popisu funkce lze vycházet z určité analogie s obvody DTL. Přechody báze-emitor vstupního tranzistoru nahrazují diody součinového hradla obvodu DTL, zatímco přechod báze-kolektor nahradí posouvací diodu. Oproti obvodům DTL jsou však mnohem příznivější podmínky na bázi tranzistoru T2. Je-li na jeden emitor vstupního tranzistoru T1 přivedena úroveň logické 0, začne tímto emitorem protékat proud v předním směru, tranzistor T1 se otevře a z báze tranzistoru T2 je velmi rychle odveden přebytečný náboj přes malou impedanci otevřeného tranzistoru T1. Tak je dosaženo velké spínací rychlosti při zavírání tranzistoru T2. Připojením všech emitorů vstupního tranzistoru na úroveň 1 bude tranzistor T1 pracovat v inverzním zapojení, t.j. zamění se funkce emitoru a kolektoru. Otevře se tranzistor T2, a to spojením báze přes otevřený přechod báze-kolektor tranzistoru T1, polarizovaným nyní v propustném směru, a přes odpor R1 se zdrojem napájecího napětí.

Výstupní obvod je zapojen jako sériový dvojčinný stupeň. Je buzen tranzistorem T2, zapojeným jako fázový invertor. V okamžiku změny hodnoty výstupní funkce obvodu jsou po velmi krátkou dobu otevřeny oba tranzistory T3 a T4. Odpor R4 v tomto případě omezuje maximální hodnotu kolektorového proudu výstupního stupně. Dioda D zajišťuje svým prahovým napětím spolehlivé uzavření tranzistoru T3. Na obrázku je upravené zapojení koncového stupně TTL obvodu, ve kterém je posouvací dioda nahrazena tranzistorem T5. Zapojení se používá pro velmi rychlé nebo výkonové logické obvody.

V ustáleném stavu je otevřen vždy pouze jeden výstupní tranzistor, takže při malém zatížení zdroje je dosaženo malé impedance jak pro úroveň 0, tak i pro úroveň 1. Výstup se velmi dobře chová při kapacitní zátěži, nízká výstupní impedance je výhodná i z hlediska vlivu parazitních signálů na činnost obvodu. To je velká přednost oproti obvodům DTL a RTL, jejichž výstupní impedance je v době uzavření tranzistoru na výstupu obvodu určena pouze jeho kolektorovým odporem.

Tags: logických, obvody, členů, 6základní, vlastnosti

- FRANÇAIS FAIRNESS FOR PARENTS AND EMPLOYEES ACT (TEACHERS’ WITHDRAWAL

- TITLE GET SMART WHEN LIFE IS RIDICULOUSLY RANDOM TEXT

- THE TIME NEEDED TO COMPLETE A FINAL EXAMINATION IN

- ♥☼☺♫♣YM ♠ ☺ JADŁOSPIS PONIEDZIAŁEK15022021 15102018 ŚNIAD 05 BUŁKI

- – 8 – PROJEKT Z DNIA 23 GRUDNIA 2019

- MANTENIMIENTO AUTÓNOMO ENRIQUE MORA UN ASPECTO MUY IMPORTANTE DEL

- CAUTOSHAPE 13 OLORADO BUREAU OF INVESTIGATION CBI LAB CASE

- DIPU 2018 UNIVERSIDAD NACIONAL DE MAR DEL PLATA FACULTAD

- REFERRAL FORM ADULT HEARING IMPLANT ASSESSMENT PLEASE NOTE DUE

- DRAFT 101008 KORDON TERMITE BARRIER PAGE 2 OF 7

- BRIEF INTERNATIONAL CURRICULUM KEY PERSONNEL FIRST NAME HECTOR FAMILY

- RC5362000 CONTRALORIA GENERAL DE LA REPUBLICA DESPACHO DEL

- BATSÁNYI JÁNOS GIMNÁZIUM ÉS SZAKKÖZÉPISKOLA A CSONGRÁDI OKTATÁSI KÖZPONT

- TRUST ELEVATION METHOD ANALYSIS TRUST ELEVATION METHOD QUESTIONS WHICH

- DEPARTMENT OF AGRICULTURE FORESTRY AND FISHERIES STD NO D1

- POWERPLUSWATERMARKOBJECT27830845 LAPORAN RINGKAS PEMANTAUAN PERATURAN KOLEJ NAMA KOLEJ KOLEJ

- TEORIA DE SISTEMAS CONCEPTOS ELEMENTALES DE SISTEMAS ENFOQUE DE

- PURA VIDA ORGANIC DOO UL JURJA DOBRILE 42 VELIKA

- SHARYLAND ISD ENGLISH IVAP 20182019 SUMMER READINGWRITING ASSIGNMENTS DEAR

- HTTPWWWUVESFRIASNAV (UNIVERSIDAD DE VALENCIA) SPAIN STATISTICS AND RESEARCH METHODS

- 2 AREA AND CLIMATE THE CZECH REPUBLIC IS A

- SCIENCE AND INDUSTRY MUSEUM L IVERPOOL ROAD CASTLEFIELD M

- POTWIERDZENIE ZWROTU KSIĄŻEK DO BIBLIOTEKI (BOOK RETURN CONFIRMATION) POTWIERDZAM

- ANEXO IIA BAREMO PROYECTOS TIPO A Y TIPO D

- O GENOGRAMU GENOGRAM JE NAČIN PREDSTAVLJANJA PORODIČNE STRUKTURE RELACIJA

- FORM 501—GENERAL INFORMATION (APPLICATION FOR RESERVATION OR RENEWAL OF

- 15A NCAC 13B 1402 GENERAL PROVISIONS FOR SOLID WASTE

- 12 12 1RETNINGSLINJER FOR PROGRAM MOT RUSPÅVIRKET KJØRING

- 3 VALSTS POLICIJAS KOLEDŽA PROGRAMMAS NOSAUKUMS JAUNĀKO TEHNOLOĢIJU IZMANTOŠANA

- ESTIMATION OF THE PROBIT MODEL FROM ANONYMIZED MICRODATA GERD

ROCKET SCIENCE AND TECHNOLOGY 4363 MOTOR AVE CULVER CITY

ROCKET SCIENCE AND TECHNOLOGY 4363 MOTOR AVE CULVER CITY ACCESIBILIDAD DE LOS PRINCIPALES MEDIOS DIGITALES DE COMUNICACIÓN ACCESIBILIDAD

ACCESIBILIDAD DE LOS PRINCIPALES MEDIOS DIGITALES DE COMUNICACIÓN ACCESIBILIDADTHEORETICAL INVESTIGATION OF THE NORMAL MODES FOR THE GROUND

COURSE NAME SOCIAL STUDIES 2202 R – RETAIN D

DISEÑO DE LOS MACROPROCESOS EN LAS EMPRESAS DE

DISEÑO DE LOS MACROPROCESOS EN LAS EMPRESAS DE HELLO EVERYONE! WELCOME TO THE GRADE 56 AREA FOR

HELLO EVERYONE! WELCOME TO THE GRADE 56 AREA FOR GOVERNMENT ENGINEERING COLLEGE JHALAWAR TEQIPIII DATE TO THE PRINCIPAL

GOVERNMENT ENGINEERING COLLEGE JHALAWAR TEQIPIII DATE TO THE PRINCIPALNA TEMELJU ČLANKA 27 I ČLANKA 51 STATUTA DOMA

NUMER SPRAWY ZP202020 ZAŁĄCZNIK NR 3 DO SIWZ WZÓR

UTENOS KOLEGIJOS NAUJOS STUDIJŲ PROGRAMOS PEDAGOGINĖ PAGALBA

UNIVERSIDAD NACIONAL DEL SUR ESCUELA NORMAL SUPERIOR “VICENTE FATONE”

UNIVERSIDAD NACIONAL DEL SUR ESCUELA NORMAL SUPERIOR “VICENTE FATONE” OVERVIEW OF ACCELERATION PROGRAM FOR ENGLISH LANGUAGE

OVERVIEW OF ACCELERATION PROGRAM FOR ENGLISH LANGUAGE CHICAGO BOTANIC GARDEN STATEMENT ON ORGANIC AND INORGANIC FERTILIZERS

CHICAGO BOTANIC GARDEN STATEMENT ON ORGANIC AND INORGANIC FERTILIZERS TI91 ¿ALQUIMIA O QUÍMICA? GUILLERMO MORENO1 ADRIÁN MORALES 2

TI91 ¿ALQUIMIA O QUÍMICA? GUILLERMO MORENO1 ADRIÁN MORALES 2PÁGINA 7 PREGUNTAS Y RESPUESTAS SOBRE LAS MÁS RECIENTES

FINAL REPORT EDOIGA09G0028 PAGE 4 OF 4 JANUARY 17

FINAL REPORT EDOIGA09G0028 PAGE 4 OF 4 JANUARY 17 EDUCACIÓN INFANTIL 5 AÑOS EI ESTÁ INICIADO

EDUCACIÓN INFANTIL 5 AÑOS EI ESTÁ INICIADO  TURIZMO VADYBOS PROGRAMOS PRISTATYMAS MOKSLEIVIAMS ĮGYVENDINANT PROJEKTĄ NPJR201310457 I

TURIZMO VADYBOS PROGRAMOS PRISTATYMAS MOKSLEIVIAMS ĮGYVENDINANT PROJEKTĄ NPJR201310457 I INSTRUCTIONS FOR UPDATING AGENCY PERFORMANCE MEASURES FISCAL YEAR 2007

INSTRUCTIONS FOR UPDATING AGENCY PERFORMANCE MEASURES FISCAL YEAR 2007INFORME Nº 9999 DIRECCION GENERAL DE AUDITORIA DEPARTAMENTO